第六章 工艺良品率

1、维持及提高良品率(yield)对半导体工业至关重要,三个主要的良品率被用来监控整个半导体工艺制程:

晶圆生产部门-良品率=晶圆产出数/晶圆投入数;

晶圆电测-良品率=合格芯片数/晶圆上的芯片总数;

封装-良品率=终测合格的封装芯片数/投入封装生产线的合格芯片数;

2、累积晶圆生产良品率:在晶圆完成所有的生产工艺后,第一个主要良品率被计算出来,称之为FAB良品率、生产线良品率、累积晶圆厂良品率或CUM良品率。要得到CUMl良品率,需要首先计算各制程站良品率(station yield=离开制程站晶圆数/ 进入制程站晶圆数),将各制程站良品率相乘即得整体的晶圆生产CUM良品率(典型值50%-90%)。

3、晶圆生产良品率的制约因素:

a.工艺制程步骤的数量;

工艺步骤增加,良率下降;工艺步骤增加同时提高了后四个制约良品率因素对制程中晶圆产生影响的可能性—数量专治。(对于商用半导体,75%的晶圆厂CUM良品率是赚取利润的底线,自动化生产线则要达到90%或以上)

b.晶圆破碎和弯曲;

手工和自动的操作、对晶圆的多次热处理、晶圆表面的平整性要求。

c.工艺制程变异;

工艺工程和工艺控制程序的目标不仅仅是保持每一个工艺操作在控制界限内,更重要的是维持相应的工艺参数稳定不变的分布。正态分布(normal distribution)+中心极限分布(central theorem distribution)

d.工艺制程缺陷;

工艺制程缺陷被定义为晶圆表面受到污染或不规则的孤立区域(或点),这些缺陷经常被称为点缺陷(spot defect),导致整个电路失效的缺陷称为致命缺陷(killer defect)。主要来源于晶圆生产区域涉及到的不同液体、气体、洁净室空气、人员、工艺设备和水等等。

e.光刻掩膜版缺陷。

一般有三种掩膜版引起的缺陷:第一种是污染物、第二种是石英板基中的裂痕、第三种是在掩膜版制作过程发生的图案变形(点、空洞、包含、突出、断裂、桥)

4、晶圆电测良品率的制约要素:

晶圆直径、 芯片尺寸(面积)、工艺制程步骤的数量、电路密度、缺陷密度、晶圆晶体缺陷密度、工艺制程周期;

a.晶圆直径和边缘芯片:增大晶圆直径可减少边缘芯片比例,对晶圆电测良品率有正面影响

b.晶圆直径和芯片尺寸:增加芯片尺寸而不增大晶圆直径将会导致晶圆表面完整芯片的比例缩小,当芯片尺寸增加时需用增大晶圆直径以维持很好的晶圆电测良品率。

c.晶圆直径和晶体缺陷(晶圆直径和工艺制程变异):增大晶圆的直径使得晶圆中心保留更多的未受影响的芯片从而提高晶圆电测良品率;

d.芯片尺寸和缺陷密度:对于给定的缺陷密度,芯片尺寸越大,良品率越低;

e. 电路密度和缺陷密度:对于给定的缺陷密度,电路密度越大,良品率越低;

f.工艺制程步骤的数量:随着工艺制程步骤数量的增加,除非采取相应措施来降低由此带来的影响,晶圆背景缺陷密度将增加,增加的背景缺陷密度会影响更多的芯片,从而使晶圆电测良品率变低;

g.特征图形尺寸和缺陷尺寸:较小的特征工艺尺寸使提高晶圆电测良品率增加了难度;

h.工艺制程周期:较长的工艺制程周期也使提高晶圆电测良品率增加了难度;

i.晶圆电测良品率公式:指数函数模型、Seeds模型、Murphy模型、负二项式模型;

5、封装和最终测试良品率:

封装工艺完成后,封装好的芯片会经过一系列的物理、环境和电性测试,总称为最终测试(final test),最终测试后得出第三个主要良品率。

6、整体工艺良品率:

整体工艺良品率是三个主要良品率的乘积,给出了出货芯片数相对最初投入晶圆上完整芯片数的百分比,它是对整个工艺流程成功率的综合评测。由特定电路的集成度、生产工艺的成熟程度(三个良品率)等决定。总体而言晶圆电测良品率是其中最低的一个环节,也是有更大提升空间的环节。

已有 1 个评论

联系站长

Email:Anndiqiu#Gmail.com

Mobile Phone:13923499497

热门文章

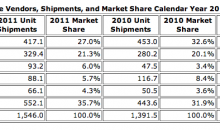

数字

$2,242.7 Million Explore Global laminating adhesives market that is poised to be worth $2,242.7 million by 2019 了解更多 »